KSZ8863RLL 3-port 10/100Mbps Ethernet switch chip

- Part No.:

- KSZ8863RLL

- Manufacturer:

- Microchip Technology

- Package:

- 48-LQFP

- Description:

- IC ETHERNET SW 3PORT 48-LQFP

- Quantity:

- Payment:

- Shipping:

Article Details

- Details

- Specifications

- Comparison

KSZ8863RLL is a three-port switch-on-a-chip from Microchip Technology, featuring the smallest package size in the industry. It is specifically designed for the next-generation Ethernet switching systems with a large number of local ports, cost-sensitive, and high energy efficiency, operating at 10/100 Mbps. It is highly suitable for applications in IPTV, IP set-top boxes (IP-STB), VoIP, automotive electronics, and industrial fields.

Notes: The three ports are typically defined as:

Port 1, Port 2: External Ethernet interfaces (RJ45 / optical ports)

Package form: 48-pin LQFP lead-free package

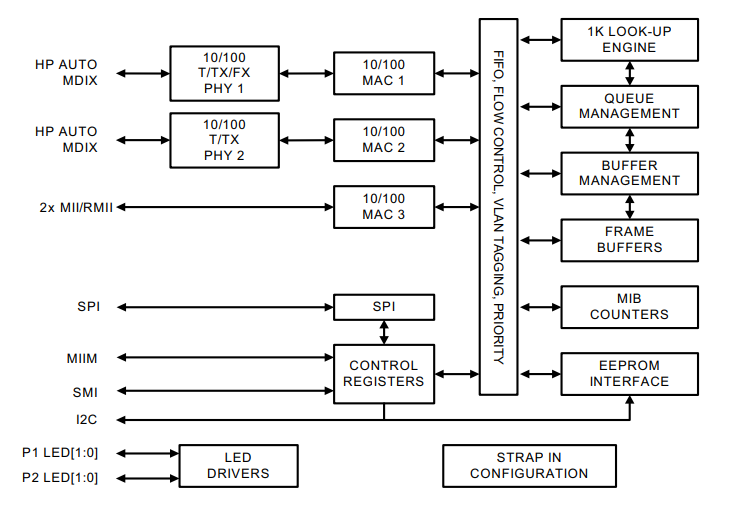

1. Overall Architecture Principles

KSZ8863 internal integration:

After the Ethernet data frame enters the switching chip, KSZ8863 processes it in the following steps:

No. KSZ8863RLL integrates 2 10/100 Mbps PHYs internally. Just connect a transformer and an RJ45 interface.

Q2: Is it necessary to connect a MCU for KSZ8863RLL to work?

Not necessarily. KSZ8863RLL supports non-managed (Unmanaged) mode. It can operate through pin bonding or EEPROM; in bypass mode, even if the MCU is in sleep or off state, ports 1 and 2 can still exchange data normally.

Q3: What are the packaging and power supply requirements for KSZ8863RLL?

Notes: The three ports are typically defined as:

Port 1, Port 2: External Ethernet interfaces (RJ45 / optical ports)

Port 3: Connection to the main processor (MII / RMII)

Get to know KSZ8863RLL

Key Features

Advanced switching function

- Supports IEEE 802.1Q VLAN (up to 16 groups, complete VLAN ID), VLAN tagging/removal, and 802.1p/q tag insertion/removal, all configurable by port

- Supports port-level ingress/egress rate limiting, broadcast storm suppression (global or port-level percentage control), and IEEE 802.1D Rapid Spanning Tree Protocol (RSTP)

- Supports tail tag mode, used to indicate the ingress port and priority of the data packet to the processor

- Supports bypass mode (Bypass), automatically maintaining normal switching of port 1 and port 2 when CPU is in sleep

- Supports MAC address filtering, self-address filtering, and port 1/2 support independent MAC addresses

- Supports IGMP Snooping (IPv4) multicast filtering and IPv4/IPv6 QoS

- Supports multiple management interface access to internal registers, including SMI, MIIM, SPI, and I²C

- Supports I/O pin binding and EEPROM configuration, suitable for non-managed switching mode

- Supports dynamic configuration of registers (port priority, 802.1p/d/q, self-negotiation, etc.)

- Supports RMII interface and provides 50 MHz reference clock output

- Supports packet priority based on port, 802.1p and DiffServ

- Supports port-level 802.1p priority remapping, providing 4-level priority queues

- Third-generation 3-port 10/100 Mbps switch, integrating 3 MAC + 2 PHY, compliant with IEEE 802.3u

- Non-blocking switching architecture, using 1K MAC address table + store-and-forward mechanism

- Supports full-duplex IEEE 802.3x flow control (PAUSE) and half-duplex backpressure flow control

- Supports Auto MDI-X and LinkMD® cable diagnosis

- Supports MII interface MAC/PHY mode, providing complete LED status indication

- HBM ESD protection level: 4 kV

- Supports port mirroring (ingress/egress) to any port or MII interface

- Provides 34 MIB statistics counters per port

- Supports loopback mode, facilitating remote fault diagnosis

- Supports chip-level power-off, port-level PHY power saving, energy detection mode

- Supports dynamic clock tree shutdown to reduce overall system power consumption

- Single 3.3V power supply, internal integrated 1.8V LDO

- VDDIO selectable 3.3V / 2.5V / 1.8V, transceiver power supply VDDA_3.3 = 3.3V

Package form: 48-pin LQFP lead-free package

The differences between KSZ8863RLL and KSZ8863MLL, KSZ8863FLL

The main differences lie in the CPU interface and port configuration:- KSZ8863MLL: Two 10/100BASE-T/TX transceivers + one MII interface

- KSZ8863RLL: Two 10/100BASE-T/TX transceivers + one RMII interface

- KSZ8863FLL: One 100BASE-FX, one 10/100BASE-T/TX transceiver + one MII interface

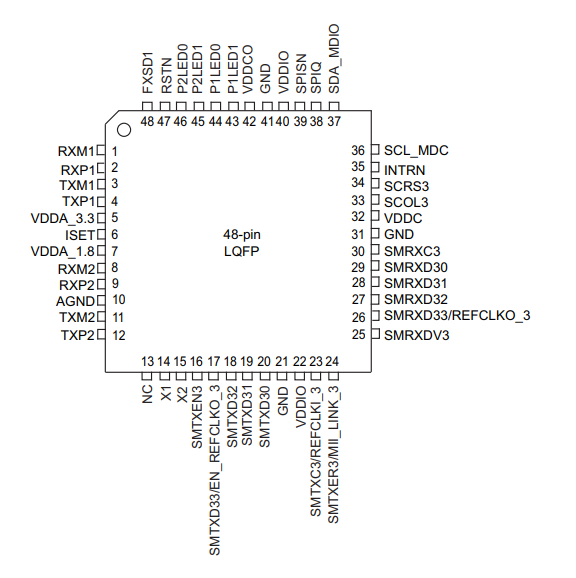

Pin description

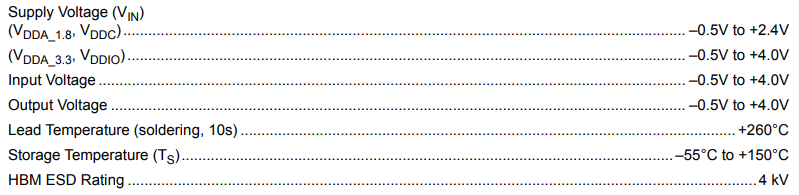

Absolute Maximum Ratings

Use KSZ8863RLL

KSZ8863 features low power consumption, advanced power management and comprehensive QoS capabilities. It is designed to meet the GREEN requirements of today's switching systems. Additionally, it provides a Bypass mode for achieving system-level energy saving.Working principle

KSZ8863 operates according to the process of link establishment - data reception - address learning and judgment - intelligent switching and forwarding - export processing - CPU collaboration or bypass operation - energy saving and monitoring.1. Overall Architecture Principles

KSZ8863 internal integration:

- 3 Ethernet MACs

- 2 10/100 Mbps PHYs

- High-speed switching fabric (Switch Fabric)

- Address lookup table (1K MAC table)

- QoS, VLAN, and flow control management module

- Power management and diagnostic unit

After the Ethernet data frame enters the switching chip, KSZ8863 processes it in the following steps:

- PHY receives data: The PHY of ports 1/2 receives the Ethernet signal from the network cable or optical fiber and automatically completes self-negotiation, rate detection, and duplex identification.

- MAC unpacking and caching: MAC receives the data frame completely, checks the FCS, and discards erroneous frames.

- Address learning and table lookup: The switching chip learns the source MAC address and writes it into the MAC table. Based on the target MAC address, it queries the forwarding table to determine the forwarding port.

- Switching fabric forwarding: Through a non-blocking switching structure, the data packet is forwarded to the target port.

- Output processing: According to the configuration, VLAN tags are inserted/removed, QoS priority scheduling, rate limiting, and flow control are executed.

- VLAN principle: Supports IEEE 802.1Q VLAN. Data packets are isolated or passed through based on the port, VLAN ID, and label rules.

- QoS principle: Classified based on 802.1p / DiffServ / IPv4 / IPv6 fields. Data frames are assigned to 4 priorities, and high-priority data is prioritized for forwarding.

- CPU interface: Port 3 is connected to the main processor via MII or RMII. The processor can participate in data transmission or be used for configuration and management.

- Bypass mode: When the processor enters sleep or power-off state, the switching chip automatically maintains the switching paths of ports 1 and 2, without relying on the CPU, ensuring that network communication is not interrupted, and achieving system-level low power consumption.

- The chip inserts a 1-byte identifier (the entry port of the data packet, priority information) before the FCS of the data frame.

- When the processor receives data through port 3, it can quickly determine the data source and priority.

- Suitable for simplifying the protocol stack processing on the CPU side.

- Full-duplex mode: Uses IEEE 802.3x PAUSE frames for flow control.

- Half-duplex mode: Uses the backpressure mechanism to avoid data conflicts.

- Auto MDI-X: Automatically identifies straight-through lines/crossed lines.

- LinkMD®: Detects network cable faults (open circuit, short circuit) through the TDR principle.

- Chip-level software power-off: Turns off core modules.

- Port-level PHY power saving: Turns off the transceiver when the link is idle.

- Energy detection mode: Automatically enters sleep mode without signal.

- Dynamic clock shutdown: Retains only necessary logic for operation.

Applications

- VoIP Phone

- Set-Top/Game Box

- Automotive

- Industrial Control

- IPTV POF

- SOHO Residential Gateway

- Broadband Gateway/Firewall/VPN

- Integrated DSL/Cable Modem

- Wireless LAN Access Point + Gateway

- Standalone 10/100 Switch

FAQ about KSZ8863RLL

Q1: Does KSZ8863RLL require an external PHY?No. KSZ8863RLL integrates 2 10/100 Mbps PHYs internally. Just connect a transformer and an RJ45 interface.

Q2: Is it necessary to connect a MCU for KSZ8863RLL to work?

Not necessarily. KSZ8863RLL supports non-managed (Unmanaged) mode. It can operate through pin bonding or EEPROM; in bypass mode, even if the MCU is in sleep or off state, ports 1 and 2 can still exchange data normally.

Q3: What are the packaging and power supply requirements for KSZ8863RLL?

- Packaging: 48-pin LQFP (lead-free, RoHS)

- Core power supply: 3.3V

- VDDIO: Supports 3.3V / 2.5V / 1.8V

- Internal integrated 1.8V LDO

- Product attributes

- Attribute value

- Manufacturer:

- Microchip Technology

- Series:

- -

- Package/Case:

- 48-LQFP

- Packaging:

- Tray

- Part Status:

- Active

- Resistance:

- Not Verified

- Tolerance:

- Ethernet

- Composition:

- I2C, SPI

- Features:

- 10/100 Base-T/TX PHY

- Temperature Coefficient:

- 1.8V, 2.5V, 3.3V

- Operating Temperature:

- -

- Supplier Device Package:

- 0°C ~ 70°C

- Power (Watts):

- Switch

- Ratings:

- 48-LQFP (7x7)

- Size / Dimension:

- -

- Height - Seated (Max):

- -

- Number of Terminations:

- Failure Rate:

| Image |  |

|

|

| Part Number | KSZ8863RLL | KSZ8863RLLI-TR | KSZ8863RLLI |

| Manufacturer | Microchip Technology | Microchip Technology | Microchip Technology |

| Package/Case | 48-LQFP | 48-LQFP | 48-LQFP |

| Programmable | Not Verified | Not Verified | Not Verified |

| Protocol | Ethernet | Ethernet | Ethernet |

| Interface | I2C, SPI | I2C, SPI | I2C, SPI |

| Standards | 10/100 Base-T/TX PHY | 10/100 Base-T/TX PHY | 10/100 Base-T/TX PHY |

| Voltage - Supply | 1.8V, 2.5V, 3.3V | 1.8V, 2.5V, 3.3V | 1.8V, 2.5V, 3.3V |

| Current - Supply | - | - | - |

| Operating Temperature | 0°C ~ 70°C | -40°C ~ 85°C | -40°C ~ 85°C |

| Function | Switch | Switch | Switch |

| Supplier Device Package | 48-LQFP (7x7) | 48-LQFP (7x7) | 48-LQFP (7x7) |

| Grade | - | - | - |

| Qualification | - | - | - |

inventory:3,736

Please send an inquiry. Send us your inquiry, and we will respond immediately.

-

PTN5150AHXMP

NXP USA Inc.

-

USB3740B-AI9-TR

Microchip Technology

-

USB3740B-AI2-TR

Microchip Technology

-

USB3300-EZK-TR

Microchip Technology

-

USB3300-EZK

Microchip Technology

-

FUSB340TMX

onsemi